Discover why NVIDIA Rubin R100 Yield 2026 is the biggest risk for AI CAPEX. Analysis of the 336B transistor wall and TSMC N2P manufacturing friction.

NVIDIA Rubin R100 Yield 2026 is the final manufacturing bottleneck for AI ROI. As the industry pushes toward a staggering 336 billion transistors on a single integrated system, the “Yield Wall” has become the defining macro risk for Big Tech’s 2026 CAPEX roadmap.

Executive Summary: The 2026 Manufacturing Crisis

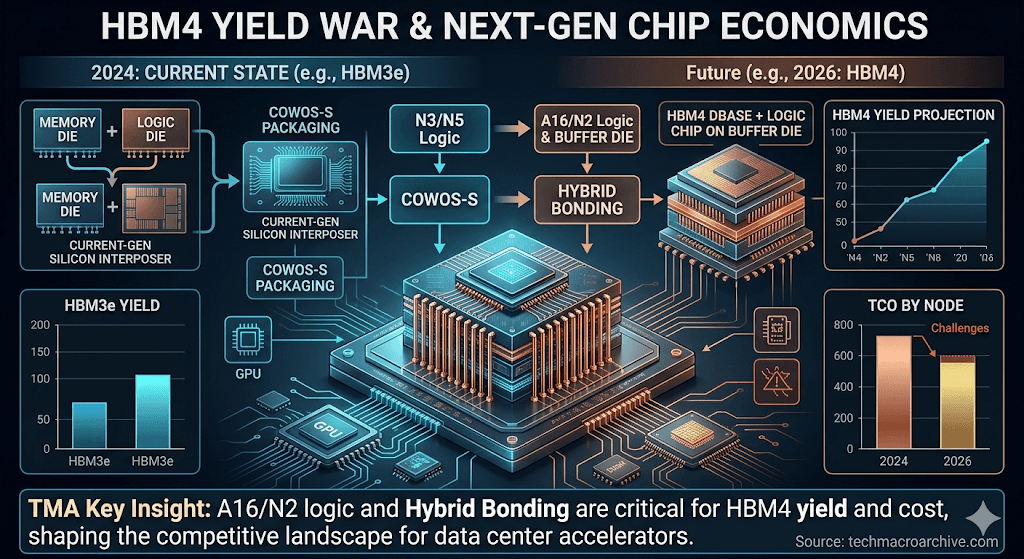

- 1. The Reticle Limit Crisis: Rubin pushes the boundaries of multi-die reticle stitching, leading to an estimated initial packaging yield of less than 60%.

- 2. Memory Integration Friction: The shift to 12-layer HBM4 integration introduces a 15% increase in “Known Good Die” (KGD) failures compared to Blackwell.

- 3. Cost Inversion: As analyzed in our report [TSMC N2P: The $32k Wafer Reality of 2026], the cost per wafer has hit an inflection point where yield loss exceeds the actual material cost.

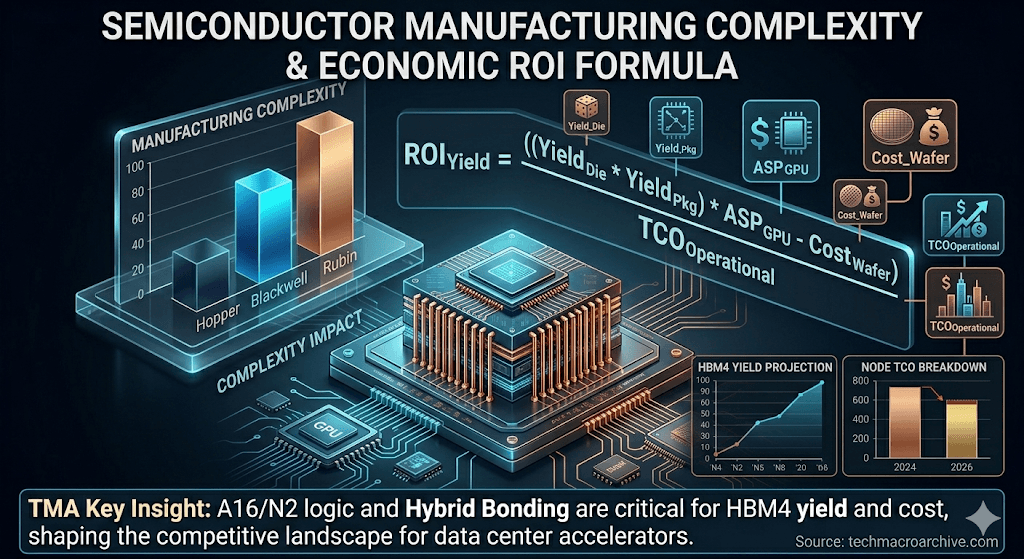

| Metric | NVIDIA Blackwell (2024/25) | NVIDIA Rubin R100 (2026) | Change |

| Transistor Count | ~208 Billion | 336+ Billion | +61% |

| Process Node | TSMC 4NP | TSMC N2P (2nm) | Shift |

| HBM Standard | HBM3E | HBM4 (12/16-layer) | Peak |

| Est. Packaging Yield | 85-90% | 55-65% (Projected) | High Risk |

The Yield Wall: Why 336B Transistors are Killing Margins

The transition to the 2nm node is a statistical nightmare. Achieving perfect lithography for 336 billion transistors on a single interposer requires precision that pushes the limits of physics. Even a 5% drop in yield at the $32,000 wafer price point results in millions of dollars in lost revenue per batch, effectively killing the margins of secondary hyperscalers.

Technical Deep-Dive & Economics ($Latex$)

The financial impact of manufacturing failure can be precisely measured by the Yield Sensitivity Formula, which links packaging defects directly to the bottom line:

As explored in our analysis of the [AI Liquid Cooling Standard 2026], these massive dies generate unprecedented heat, further complicating the validation phase. Minor substrate defects that pass initial tests often fail under the extreme thermal stress required for HBM4 performance, as detailed in our [HBM4 Thermal Redline] report.

“The R100 isn’t just a GPU; it’s a packaging nightmare. 2026 will be remembered as the year HBM4 integration made or broke AI giants.” — [Semiconductor Insight 2026]

2026 Investment Strategy: The “Yield Winners”

While NVIDIA faces supply constraints, capital is rotating into the infrastructure layer that solves the yield crisis:

- SK Hynix: Providing “Zero-Defect” HBM4 stacks to minimize packaging-level failures.

- Teradyne (TER): Dominating the complex testing environment required for 336B transistor chips.

- Samsung Electronics: Positioned as the critical secondary foundry if TSMC N2P capacity remains yield-constrained.

Conclusion: Will the Market Absorb the Cost?

The 2026 AI battle is being fought on the factory floor. The NVIDIA Rubin R100 Yield 2026 will determine which hyperscalers survive the $700B CAPEX sprint and which ones are buried by the cost of manufacturing complexity.

Related Tech Insights:

- [TSMC N2P Mass Production: The $32k Wafer Reality of 2026]

- [AI Liquid Cooling Standard 2026: The $200B Infrastructure War]

- [HBM4 Thermal Redline: Why 2026 AI ROI Depends on Cooling]

Sharp Question:

If yield rates don’t hit 75% by 2027, will the “Infinite Compute” dream collapse under its own manufacturing weight?

NVIDIA Rubin R100, 2nm Yield Crisis, TSMC N2P, HBM4 Integration, Advanced Packaging,