HBM4 Foundry Integration: The End of Standalone Memory in the 2026 AI Era

The arrival of HBM4 has fundamentally altered the semiconductor hierarchy, as the requirement for “Foundry-Logic” base dies forces a radical integration of memory and logic through Hybrid Bonding. In 2026, the bottleneck is no longer just stacking memory layers; it is the physical and economic challenge of fusing a TSMC-manufactured logic controller with a 16-layer memory stack from SK Hynix or Micron.

Executive Summary: The Logic-Memory Convergence

- 1. The Logic Shift: Unlike HBM3E, HBM4’s base die must be fabricated on 5nm/7nm logic nodes to handle the massive I/O required for the 2026 Rubin architecture.

- 2. Hybrid Bonding Hegemony: Traditional Micro-bumps are too bulky for the required interconnect density, making Cu-to-Cu Hybrid Bonding the only viable path for Foundry-Memory fusion.

- 3. Yield Responsibility: A new legal and economic friction has emerged—who pays for the loss when a perfectly good logic die is ruined during the hybrid bonding of a faulty memory stack?

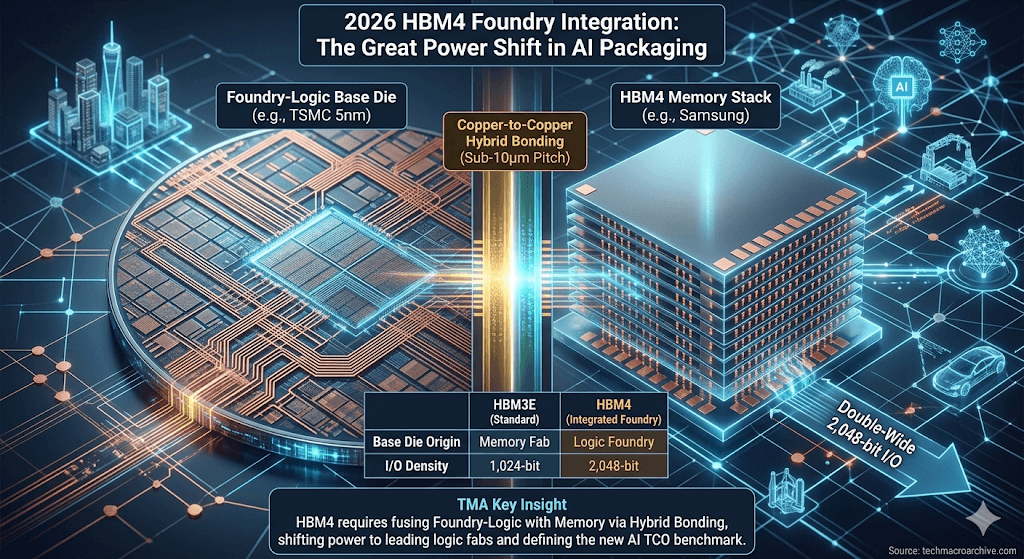

| Integration Metric | HBM3E (Standard) | HBM4 (Integrated Foundry) |

| Base Die Origin | Memory Fab (Legacy Node) | Logic Foundry (Advanced Node) |

| Interconnect Method | Micro-bumps (Solder) | Hybrid Bonding (Copper-to-Copper) |

| I/O Density | 1,024-bit | 2,048-bit (Double-wide) |

| Supply Chain Power | Memory Provider Dominant | Foundry-OSAT Co-dominance |

1: The 2048-bit I/O Wall

The 2026 AI roadmap demands a doubling of I/O density. As noted in our previous analysis on HBM4 Yield Crisis, the transition is not merely incremental. By moving to a 2048-bit interface, HBM4 requires more interconnects in the same footprint. This physical reality forces the industry toward Hybrid Bonding, where the pitch is reduced below 10µm. This “Foundry Integration” is now the primary lever for reducing Total Cost of Ownership (TCO) in AI clusters.

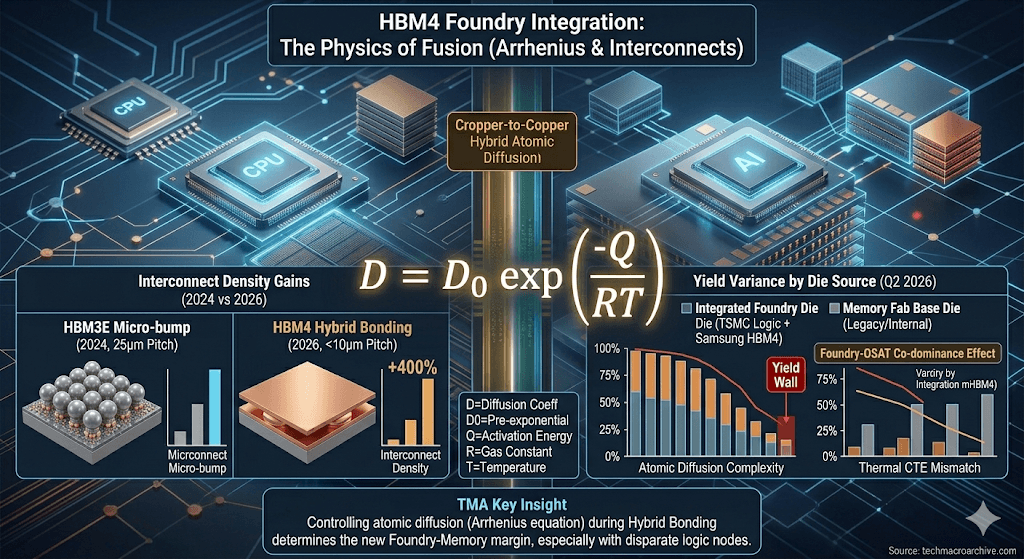

2: Atomic Diffusion & The Physics of Fusion

The technical heart of this integration is the atomic diffusion between the copper pads of the logic die and the memory stack. To achieve a stable bond, the surface must be polished to sub-nanometer roughness, and the temperature must be precisely controlled to facilitate the Arrhenius-governed diffusion process:

Where $D$ is the diffusion coefficient. If the Foundry die and the Memory die have different thermal expansion coefficients (CTE), the $R_{interface}$ increases, leading to the “Yield Wall” we see in Q2 2026. This technical friction is creating a new power dynamic between TSMC (the logic source) and the HBM titans.

“The HBM4 era turns memory into a ‘peripheral of the logic die.’ If you don’t control the bonding interface, you don’t control the margin.” — By TMA

3: Geopolitical OSAT Shifts

This integration is also re-wiring the map. As highlighted in The Great Semiconductor Migration, the need for ultra-high-end cleanrooms for hybrid bonding is concentrating power back into advanced hubs (Taiwan, Korea, USA). The complexity of integrating a TSMC logic die with a Samsung memory stack is not just a technical hurdle; it’s a logistical and geopolitical nightmare of “Friend-shoring” and IP protection.

Conclusion: The Era of the “System-in-Stack”

HBM4 is no longer just “memory”—it is a complex, multi-die system. The winners of 2026 will be those who can navigate the “Foundry Integration” bottleneck, successfully fusing disparate silicon from different fabs into a single, high-yield vertical pillar.

Related Tech Insights:

- [NVIDIA Rubin R100 Yield 2026: The 336B Transistor Wall]

- [The HBM4 Yield Crisis: Why Logic Integration is the New Bottleneck]

- [TSMC N2P Mass Production: The $32k Wafer Reality of 2026]

Sharp Question:

As memory becomes physically fused to logic via hybrid bonding, will we see the rise of “Total Foundry” players who refuse to bond third-party memory, effectively monopolizing the AI stack?

HBM4 Foundry, Hybrid Bonding Yield, AI Interconnect, Logic-Memory Fusion, 2026 Semiconductor Macro,