The $32,000 Wafer Crisis: The Brutal Economics of 2nm & High-NA EUV

In 2026, the semiconductor industry has hit a financial wall that is arguably more formidable than the laws of physics. As TSMC and Intel push into the 2nm and 1.4A era, the price of a single processed wafer has skyrocketed to an eye-watering $32,000. This isn’t just inflation; it’s a fundamental shift in the silicon hierarchy.

Executive Summary

The transition to 2nm nodes, powered by ASML’s High-NA EUV lithography, has created a “Yield-Cost Paradox.” While the performance gains are undeniable, the capital expenditure required to maintain these nodes is forcing a consolidation of the client base to only those with the deepest pockets.

| Metric | 7nm (2018) | 5nm (2020) | 3nm (2023) | 2nm (2026 Est.) |

| Wafer Price | ~$10,000 | ~$16,000 | ~$20,000 | $30,000 – $32,000 |

| Transistor Density | 1.0x | 1.8x | 2.5x | 3.1x |

| Key Tech | DUV/EUV | EUV | FinFET/GAA | NanoSheet / BSPDN |

1. The High-NA Tax: Why Moore’s Law is Now a Luxury Goods Market

The primary driver of the $32,000 price tag is the ASML High-NA EUV monopoly 2026. Each EXE:5200 machine now costs upwards of $400 million. When you factor in the lower depth of focus and the requirement for new photoresists and masks, the “cost per exposure” has doubled compared to standard EUV.

Foundries are struggling with the 2nm yield gap, where even a 1% fluctuation in yield can result in hundreds of millions of dollars in lost revenue. This has turned the semiconductor landscape into a high-stakes poker game where only Apple, NVIDIA, and perhaps one or two others can afford to sit at the table.

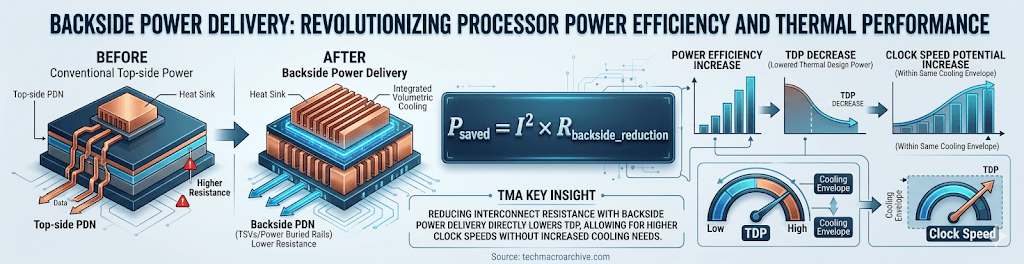

2. BSPDN and the Power Delivery Revolution

To justify the astronomical costs of 2nm, the architecture must solve the “Resistance Wall.” In traditional designs, power delivery and signal routing compete for space on the top layers, leading to significant IR drop (voltage sag) and routing congestion.

TSMC is accelerating its N2P node specifically to integrate BSPDN(Backside Power Delivery Network). By relocating the power distribution to the reverse side of the wafer, designers can decouple power and signal, effectively eliminating the “Front-side Traffic Jam.”

“The A16 Super Power Rail is not just an architectural choice; it is a survival mechanism to ensure that the $32,000 spent on the wafer yields enough performance to satisfy the AI era’s insatiable demand.” — TMA Senior Analyst

3. The TCO Trap for AI Startups

While giants like Apple utilize the A20 Pro to maintain margins, the rest of the industry faces a “Design Gap.” The cost of designing a 2nm chip has surpassed $1 billion when including IP licensing and validation. This creates a barrier to entry that might permanently stall the “Custom ASIC” dreams of mid-sized AI firms, forcing them back into the arms of the major CSPs.

Conclusion: The End of “Cheap” Scaling

The A16 node proves that the “free lunch” of Moore’s Law is over. We have entered an era where performance is bought with architectural complexity and massive capital investment.

[TMA Archive: Internal Link Power]

Sharp Question: As the gap between “Backside Power” chips and standard silicon widens, will 2026 mark the year where the “Base” iPhone becomes a legacy device in an Agentic AI world?

2nm Yield Crisis, High-NA EUV Cost, TSMC N2P, Apple A20 Pro, Semiconductor TCO