TSMC N2P HVM begins. With BSPDN adding a 35% cost premium, only Apple and NVIDIA survive. Explore the 2026 2nm ROI crisis and the “Backside Power Tax.”

TSMC N2P Mass Production: The Brutal Economics of BSPDN in 2026

Executive Summary: As of April 14, 2026, the semiconductor industry has hit a wall where traditional scaling no longer yields profit. TSMC’s N2P (2nm Performance) process has officially moved to high-volume manufacturing (HVM). However, this is a $32,000-per-wafer gatekeeper that is fundamentally bifurcating the AI industry into those who can afford the “Backside Power Tax” and those relegated to legacy silicon.

[Comparison: The Price of Performance 2026]

| Metric | N3P (3nm) | N2 (Base 2nm) | N2P (2nm + BSPDN) |

|---|---|---|---|

| Logic Density | 1.0x | 1.15x | 1.15x |

| Power Efficiency | Ref | +15% | +25-30% |

| Est. Wafer Price | $21,000 | $28,500 | $32,000+ |

| Primary Bottleneck | EUV Multi-patterning | NanoSheet Yield | Hybrid Bonding Precision |

The Core Friction: Performance at the Cost of Insolvency

The market is currently hallucinating a seamless transition to 2nm. Data from the first half of 2026 suggests otherwise. While N2P delivers the promised 10-12% speed boost over base N2, the introduction of BSPDN (Backside Power Delivery Network) has moved the “Market Friction” from physics to finance.

By moving power rails to the back of the wafer, TSMC has eliminated the signal interference that plagued the N3 era. However, the complexity of thinning the wafer to sub-micrometer levels and connecting it with Through-Silicon Vias (TSVs) has created a “Yield Wall.” For any firm outside the “Trillion Dollar Club,” the ROI on N2P is currently negative.

Technical Deep-Dive & Economics

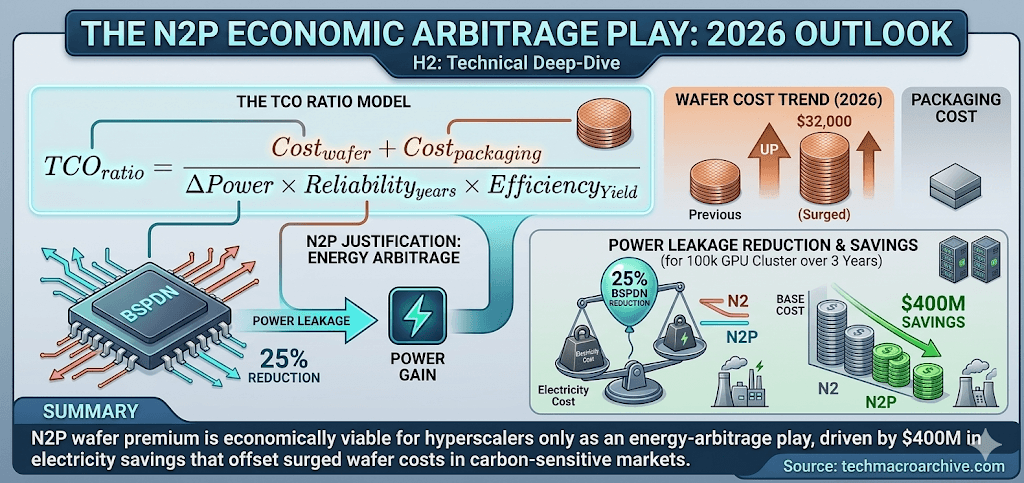

The economic viability of N2P is governed by the Total Cost of Ownership ($TCO$) for hyperscalers. The justification for the N2P premium is an energy-arbitrage play, modeled by the following ratio:

In 2026, while the wafer cost has surged to $32,000, the power leakage reduction via BSPDN is approximately 25%. For NVIDIA’s 2026 “Rubin” architecture, this translates to a $400M reduction in electricity costs per 100k GPU cluster over three years. This efficiency gain is the only reason N2P exists in a market sensitive to carbon taxes and grid limits.

“The N2P ramp is the most capital-intensive transition in our history. BSPDN is no longer a luxury; it is the only way to bypass the thermal throttling of HBM4.” — TSMC Q1 2026 Earnings Call

2026 Investment Strategy: The N2P Hegemony

The winners and losers of the 2026 N2P era are already etched into the supply chain:

- The Winners (The “N2P Elite”):

- AAPL: Secured 80% of initial N2P capacity for the iPhone 18 Pro (A20 Pro).

- NVDA: Utilizing N2P for “Rubin Ultra” to maintain the lead over custom ASICs.

- The Losers (The “2nm Trap”):

- INTC: Despite “Intel 14A” claims, they struggle with High-NA EUV integration costs compared to TSMC’s refined N2P yield.

- QCOM: Forced to stick with N3P for mid-tier chips, widening the performance gap.

Forward Risk: The Hybrid Bonding Bottleneck

The “Black Swan” for 2026 is the Hybrid Bonding Bottleneck. N2P requires extreme precision in wafer-to-wafer bonding. If the equipment downtime from vendors exceeds 15%, TSMC’s “Golden Yield” will collapse, leading to a massive shortage of AI accelerators in Q4 2026.

Conclusion: Is the 25% Power Gain Worth a 50% Price Hike?

The N2P transition isn’t just a technical upgrade; it’s a financial filter that will define the next decade of AI dominance. Only those who can afford the “Backside Power Tax” will survive the next wave of the LLM arms race.

[TMA Archive: Internal Link Power]

- [The 2nm Yield Trap: Why Efficiency is the New Scarcity in 2026]

- [The Backdoor Revolution: BSPDN and the Great Recalibration]

- [HBM4 Thermal Redline: Why 2026 AI ROI Depends on Cooling]

The Sharp Question

As TSMC tightens its grip on the 2nm landscape, we must ask: Have we reached the point where only three companies on Earth can afford the cutting edge of silicon?

TSMC N2P, BSPDN (Backside Power Delivery), $32,000 Wafer, Mass Production 2026, AI Infrastructure TCO,