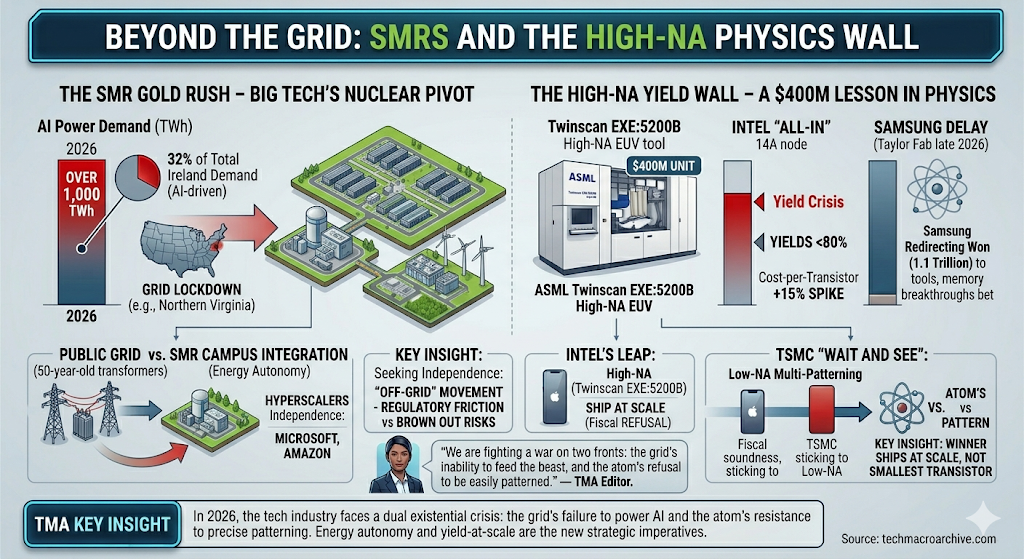

Exploring the two critical bottlenecks of 2026: The desperate pivot to Small Modular Reactors (SMRs) for AI power and the brutal yield struggles of High-NA EUV lithography.

Analysis 1: The SMR Gold Rush – Big Tech’s Pursuit of Energy Sovereignty

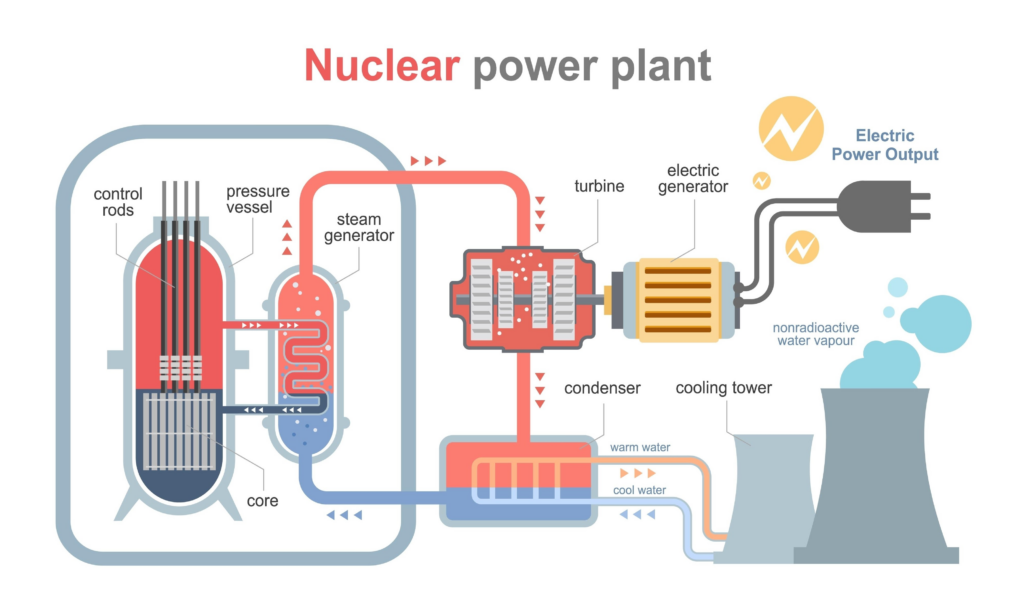

The year 2026 marks the definitive end of the “Software-Only” era for Big Tech. As AI inference loads drive global data center power consumption toward the 1,000 TWh threshold, the public grid has reached its structural breaking point. Small Modular Reactors (SMRs) have transitioned from academic curiosity to a strategic necessity for survival.

We are witnessing a desperate “Off-grid” movement. Hyperscalers like Microsoft, Amazon, and Google are no longer mere electricity consumers; they are redefining themselves as Energy Producers. By integrating SMRs directly into data center campuses and investing in the HALEU (High-Assay Low-Enriched Uranium) supply chain, these titans are seeking Energy Sovereignty—independence from aging state utilities and 50-year-old transformers that cannot keep pace with the AI revolution.

However, the “On-site Atom” is not a silver bullet for the immediate 2026 brownout risks. Regulatory friction and cooling infrastructure requirements remain significant hurdles. The winner in this era isn’t just who has the best model, but who secures the most stable, carbon-free gigawatts.

“While SMRs promise independence from the centralized power grid, the geopolitical instability of the HALEU (High-Assay Low-Enriched Uranium) supply chain is dragging Big Tech back into the vortex of a global resource war.”

Analysis 2: The High-NA Yield Wall – A $400M Lesson in Economic Physics

While the media remains obsessed with “1.4nm” headlines, the reality inside the world’s leading fabs is grim. Intel’s “All-in” bet on ASML’s High-NA EUV (Twinscan EXE:5200B) is hitting the inevitable wall of economics. At $400 million per unit, the math for High-NA only works if yields exceed the 80% threshold—a figure that remains elusive for sub-2nm processes in early 2026.

The industry is facing a “Profitability Cliff.” While High-NA reduces process steps compared to Low-NA multi-patterning, the staggering depreciation costs and mask replacement frequencies have spiked the cost-per-wafer by an estimated 18-22%. Samsung’s delay of its Taylor fab prototype to late 2026 is a silent admission of this Yield Crisis. Meanwhile, TSMC’s “Wait and See” approach—squeezing the limits of Low-NA for as long as possible—is proving to be the more fiscally sound strategy. In 2026, supremacy is not defined by the smallest transistor, but by the ability to ship functional silicon at scale without collapsing margins.

“To bypass the yield cliff of High-NA EUV, Nvidia and Apple are staking their future on chiplet-based packaging architectures rather than relying on monolithic, large-scale single dies.”

TMA Fact Check 2026

- The Energy Gap: The IEA reports that AI-driven demand now accounts for 32% of Ireland’s total electricity demand, a harbinger of the “Grid Lockdown” now facing Northern Virginia and West London.

- The Intel Leap: Intel has successfully deployed its second High-NA system for the 14A node, but initial mask defects have caused “Cost-per-Transistor” to spike by 15%, testing the patience of its foundry customers.

- The Memory-Logic Merger: Samsung has redirected 1.1 trillion won to secure High-NA tools for both 2nm logic and HBM4 (6th Gen). They are betting that the “Memory Wall” breakthrough—placing HBM directly on the logic die—will offset the agonizing yield pains of the 2nm process.

Related Deep Analysis

- The Yield War: Samsung’s 2nm Struggle and Micron’s HBM4 Coup

- Algorithmic Sovereignty: Why Nations are Building Sovereign AI Clouds in 2026

The Sharp Question

If the “Cost-per-Intelligence” begins to rise because of energy and yield constraints, will the AI bubble finally burst, or will we accept a world where only the top 0.1% of enterprises can afford frontier-model compute?

#SMR #NuclearEnergy #HighNA_EUV #Intel #Samsung #TSMC #AI_Infrastructure