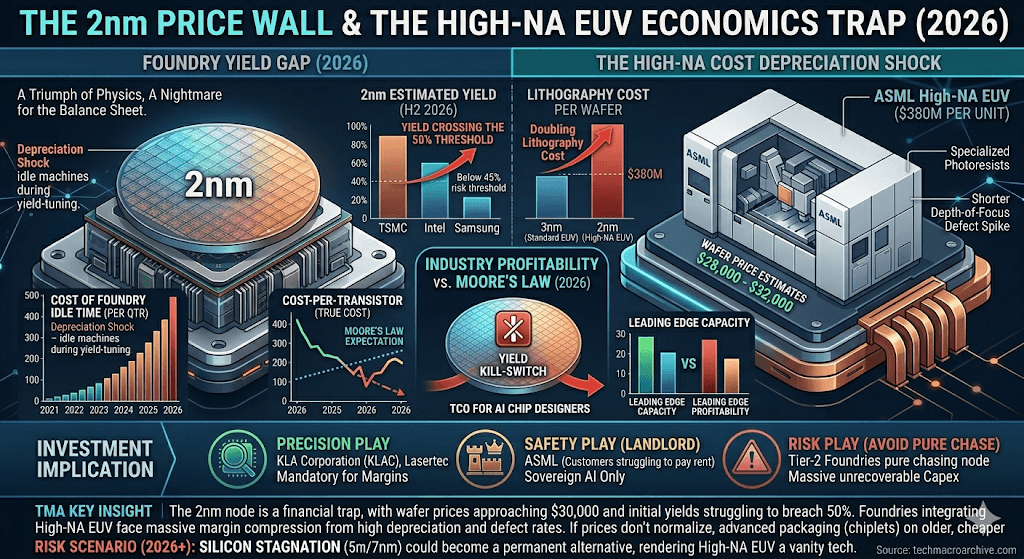

2nm wafer prices are hitting $30,000. Is High-NA EUV an economic trap? Analysis of 2026 foundry yields, Intel 18A, and the death of Moore’s Law.

The semiconductor industry is hitting a “Price Wall.” While the technical community celebrates the deployment of ASML’s High-NA EUV (EXE:5000) systems, the financial reality for foundries in 2026 is terrifying. With 2nm Wafer Price projections breaching the $30,000 mark, we are entering an era where only the most elite “Sovereign AI” projects can afford to exist.

Executive Summary

- The Cost Explosion: A single High-NA EUV scanner now costs over $380M, doubling the lithography cost-component per wafer compared to 3nm.

- The Yield Trap: Initial 2nm yields are struggling to cross the 50% threshold, effectively doubling the “real” cost for chip designers.

- Investment Implication: Focus on firms that control the metrology and inspection niche; as wafer prices rise, the cost of “bad chips” becomes an existential threat to margins.

The Core Friction: Resolution vs. ROI

The market assumes that better resolution (0.55 NA) automatically equates to better business. It doesn’t. In 2026, the friction lies in the Depreciation Shock. Foundries like Intel and Samsung, who integrated High-NA early to leapfrog TSMC, are finding that the throughput of these machines hasn’t scaled linearly with their cost. For the first time, the “Cost-per-Transistor” is trending upward, breaking a 50-year streak of Moore’s Law economics.

Why the Market Is Mispricing This

Analysts are still valuing foundries based on “Leading Edge Capacity” rather than “Leading Edge Profitability.” They overlook the Mask Count Paradox. While High-NA reduces the number of exposures (double-patterning), the specialized photoresists and shorter depth-of-focus are causing a spike in defect rates. The market has yet to price in the massive margin compression coming in the second half of 2026 as these $380M machines sit idle during yield-tuning phases.

Data, Yield, and Cost Reality

The 2026 foundry landscape is divided by a “Yield Gap” that is wider than any previous node transition.

- 2nm Estimated Wafer Price: $28,000 – $32,000 (compared to ~$20,000 for 3nm).

- High-NA Throughput: 150-180 wafers per hour (Estimated 2026 target).

- The Kill-Switch: If yield stays below 45% for more than two quarters, the TCO (Total Cost of Ownership) for an AI chip designer becomes higher than the projected revenue, leading to order cancellations.

Investment Implications

- The “Safety” Play: ASML remains the only landlord, but their customers (Foundries) are struggling to pay the rent.

- The “Precision” Play: KLA Corporation (KLAC) and Lasertec. In a $30,000 wafer environment, inspection is not an option; it is a mandate. One speck of dust now costs more than a luxury car.

- The Risk: Avoid foundries that are purely “chasing the node” without a locked-in “Sovereign AI” buyer who is price-insensitive (e.g., government-backed data centers).

Forward Risk Scenario (2026+)

The ultimate risk is the “Silicon Stagnation.” If 2nm Wafer Prices do not normalize by 2027, the industry may pivot toward “Advanced Packaging” (Chiplets) on older, cheaper nodes (5nm/7nm) as a permanent alternative. This would turn High-NA EUV into a “Vanity Tech” used only for ultra-low-power mobile flagships, leaving foundries with massive, unrecoverable Capex.

Conclusion

Technology has outpaced economics. The 2nm node is a triumph of physics but a nightmare for the balance sheet. As we navigate 2026, the winners won’t be those with the smallest transistors, but those who can actually afford to build them.

Citations

- “High-NA EUV systems expected to reach $380M per unit by 2026.” — Reuters / ASML IR

- “2nm node wafer costs projected to increase by 50% over 3nm.” — [IC Insights / TechInsights Analysis]

Internal Linking

- 2nm Yield Rates 2026: Why TSMC is starving the market to protect its own margins.

- Tungsten Supply Chain 2026: The material bottleneck threatening 2nm productivity.

- Glass Substrate Commercialization: The packaging solution that might save us from the 2nm cost trap.

Monetization Layer

- Comparison: Intel 18A (High-NA First) vs. TSMC N2 (Standard EUV Extension).

- Ranking: 2026 Margin Resilience: 1. TSMC (Conservative), 2. Intel (Aggressive), 3. Samsung (High-Risk).

- Decision Trigger: Watch for “Yield Achievement” announcements in Q3 2026; if silent, sell foundry stocks.

Sharp Question: If a chip costs $30,000 to bake, but the market only pays for a $500 performance gain, who blinks first?

2nm Wafer Price, High-NA EUV, ASML EXE:5000, 2nm Yield Gap, Intel 18A.